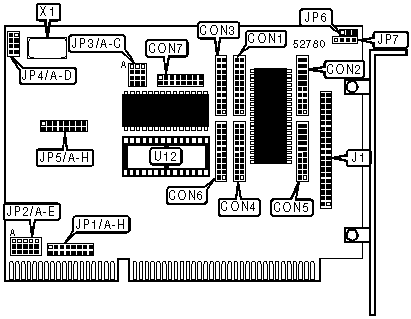

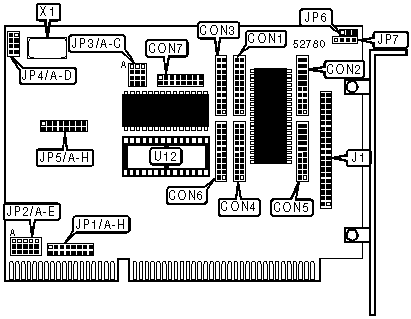

ACQUTEK CORPORATION

PI-IO48A

|

Card Type |

Multi-I/O |

|

Chipset |

Unidentified |

|

Maximum Onboard Memory |

32KB SRAM/NVSRAM/EEPROM or 64KB EPROM |

|

I/O Options |

Digital I/O (6), control interface, timer I/O |

|

Data Bus |

8/16 bit ISA |

|

CONNECTIONS | |||

|

Function |

Label |

Function |

Label |

|

Digital XDI I/O module connector 1 |

CON1 |

Digital XDI I/O module connector 5 |

CON5 |

|

Digital XDI I/O module connector 2 |

CON2 |

Digital XDI I/O module connector 6 |

CON6 |

|

Digital XDI I/O module connector 3 |

CON3 |

Timer I/O connector (see pinout below) |

CON7 |

|

Digital XDI I/O module connector 4 |

CON4 |

Digital XCI control connector |

J1 |

|

CON7 PINOUT | |||

|

Function |

Pin |

Function |

Pin |

|

Clock 2 signal in |

1 |

Clock 0 signal in |

9 |

|

Ground |

2 |

Ground |

10 |

|

Gate 2 signal out |

3 |

Gate 0 signal out |

11 |

|

Clock 2 signal out |

4 |

Clock 0 signal out |

12 |

|

Clock 1 signal in |

5 |

Not used |

13 |

|

Ground |

6 |

Not used |

14 |

|

Gate 1 signal out |

7 |

Not used |

15 |

|

Clock 1 signal out |

8 |

Not used |

16 |

|

USER CONFIGURABLE SETTINGS | ||

|

Setting |

Label |

Position |

|

U12 memory enabled |

JP4/A |

Open |

|

U12 memory disabled |

JP4/A |

Closed |

|

BASE I/O ADDRESS SELECTION | |||||||||

|

Setting |

JP1/A |

JP1/B |

JP1/C |

JP1/D |

JP1/E |

JP1/F |

JP1/G |

JP1/H | |

|

000h |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed | |

|

010h |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Open | |

|

020h |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Open |

Closed | |

|

030h |

Closed |

Closed |

Closed |

Closed |

Closed |

Closed |

Open |

Open | |

|

040h |

Closed |

Closed |

Closed |

Closed |

Closed |

Open |

Closed |

Closed | |

| � |

2E0h |

Closed |

Closed |

Open |

Closed |

Open |

Open |

Open |

Closed |

|

FB0h |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

Open | |

|

FC0h |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

Closed | |

|

FD0h |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

Open | |

|

FE0h |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Closed | |

|

FF0h |

Open |

Open |

Open |

Open |

Open |

Open |

Open |

Open | |

|

Note: A total of 256 base address settings are available. The jumpers are a binary representation of the decimal memory addresses. JP1/A is the Most Significant Bit and jumper JP1/H is the Least Significant Bit. The jumpers have the following decimal values: JP1/A=2048, JP1/B=1024, JP1/C=512, JP1/D=256, JP1/E=128, JP1/F=64, JP1/G=32, JP1/H=16. Open the jumpers and add the values of the jumpers that are open to obtain the correct memory address. (Open=1, Closed=0) | |||||||||

|

INTERRUPT SOURCE SELECTION | ||

|

Setting |

JP6 |

JP7 |

|

From host computer |

Pins 1 & 2 closed |

Open |

|

From XCI modules |

Pins 2 & 3 closed |

Pins 2 & 3 closed |

|

Note:When the interrupt source is set to the XCI modules, jumper JP2 has no effect. | ||

|

INTERRUPT SELECTION | |||||

|

Setting |

JP2/A |

JP2/B |

JP2/C |

JP2/D |

JP2/E |

|

IR/FONT> |

Open |

Open |

Open |

Open |

Pins 2 & 3 |

|

IRQ3 |

Open |

Open |

Open |

Pins 2 & 3 |

Open |

|

IRQ4 |

Open |

Open |

Pins 2 & 3 |

Open |

Open |

|

IRQ5 |

Open |

Pins 2 & 3 |

Open |

Open |

Open |

|

IRQ7 |

Pins 2 & 3 |

Open |

Open |

Open |

Open |

|

IRQ10 |

Open |

Open |

Open |

Open |

Pins 1 & 2 |

|

IRQ11 |

Open |

Open |

Open |

Pins 1 & 2 |

Open |

|

IRQ12 |

Open |

Open |

Pins 1 & 2 |

Open |

Open |

|

IRQ14 |

Open |

Pins 1 & 2 |

Open |

Open |

Open |

|

IRQ15 |

Pins 1 & 2 |

Open |

Open |

Open |

Open |

|

Disabled |

Open |

Open |

Open |

Open |

Open |

|

Note:Pins designated are in the closed position. | |||||

|

CLOCK 0 INPUT SOURCE | |

|

Setting |

JP3/C |

|

Pin 5 of CON7 |

Open |

|

Internal 3.58MHz clock |

Pins 3 & 4 closed |

|

X1 crystal |

Pins 1 & 2 closed |

|

CLOCK 1 INPUT SOURCE | |

|

Setting |

JP3/B |

|

Pin 3 of CON7 |

Open |

|

Internal 3.58MHz clock |

Pins 3 & 4 closed |

|

X1 crystal |

Pins 1 & 2 closed |

|

CLOCK 2 INPUT SOURCE | |

|

Setting |

JP3/A |

|

Pin 1 of CON7 |

Open |

|

Internal 3.58MHz clock |

Pins 3 & 4 closed |

|

X1 crystal |

Pins 1 & 2 closed |

|

MEMORY CONFIGURATION | |

|

Size |

U12 |

|

8KB EPROM |

(1) 2764 |

|

8KB EEPROM |

(1) 2864 |

|

8KB SRAM |

(1) 6264 |

|

8KB NVSRAM |

(1) 4010 |

|

16KB EPROM |

(1) 27128 |

|

32KB EPROM |

(1) 27256 |

|

32KB EEPROM |

(1) 28256 |

|

32KB SRAM |

(1) 62256 |

|

32KB NVSRAM |

(1) 4011 |

|

64KB EPROM |

(1) 27512 |

|

MEMORY JUMPER CONFIGURATION | |||

|

Size |

JP5/A |

JP5/B |

JP5/C |

|

8KB EPROM |

Closed |

Closed |

Open |

|

8KB EEPROM |

Closed |

Closed |

Closed |

|

8KB SRAM |

Closed |

Closed |

Closed |

|

8KB NVSRAM |

Closed |

Closed |

Closed |

|

16KB EPROM |

Open |

Closed |

Open |

|

32KB EPROM |

Closed |

Open |

Open |

|

32KB EEPROM |

Closed |

Open |

Closed |

|

32KB SRAM |

Closed |

Open |

Closed |

|

32KB NVSRAM |

Closed |

Open |

Closed |

|

64KB EPROM |

Open |

Open |

Open |

|

SHARED MEMORY ADDRESS SELECTION | ||||||

|

Setting |

JP4/B |

JP4/C |

JP4/D |

JP5/D |

JP5/E |

JP5/F |

|

C0000h |

Closed |

Open |

Open |

Closed |

Closed |

Closed |

|

C2000h |

Closed |

Open |

Open |

Open |

Closed |

Closed |

|

C4000h |

Closed |

Open |

Open |

Closed |

Open |

Closed |

|

C6000h |

Closed |

Open |

Open |

Open |

Open |

Closed |

|

C8000h |

Closed |

Open |

Open |

Closed |

Closed |

Open |

|

CA000h |

Closed |

Open |

Open |

Open |

Closed |

Open |

|

CC000h |

Closed |

Open |

Open |

Closed |

Open |

Open |

|

CE000h |

Closed |

Open |

Open |

Open |

Open |

Open |

|

D0000h |

Open |

Closed |

Open |

Closed |

Closed |

Closed |

|

D2000h |

Open |

Closed |

Open |

Open |

Closed |

Closed |

|

D4000h |

Open |

Closed |

Open |

Closed |

Open |

Closed |

|

D6000h |

Open |

Closed |

Open |

Open |

Open |

Closed |

|

D8000h |

Open |

Closed |

Open |

Closed |

Closed |

Open |

|

DA000h |

Open |

Closed |

Open |

Open |

Closed |

Open |

|

DC000h |

Open |

Closed |

Open |

Closed |

Open |

Open |

|

DE000h |

Open |

Closed |

Open |

Open |

Open |

Open |

|

E0000h |

Open |

Open |

Closed |

Closed |

Closed |

Closed |

|

E2000h |

Open |

Open |

Closed |

Open |

Closed |

Closed |

|

E4000h |

Open |

Open |

Closed |

Closed |

Open |

Closed |

|

E6000h |

Open |

Open |

Closed |

Open |

Open |

Closed |

|

E8000h |

Open |

Open |

Closed |

Closed |

Closed |

Open |

|

EA000h |

Open |

Open |

Closed |

Open |

Closed |

Open |

|

EC000h |

Open |

Open |

Closed |

Closed |

Open |

Open |

|

EE000h |

Open |

Open |

Closed |

Open |

Open |

Open |

|

MEMORY WRITE PROTECT CONFIGURATION | ||

|

Setting |

JP5/G |

JP5/H |

|

Enabled |

Open |

Open |

|

Disabled |

Open |

Closed |

|

Controlled by PC27 signal of 82c255 chip |

Closed |

Open |